Addressing Performance and Reliability Concerns with Thermal Analysis for RF Power Applications

Kristoffer Sander Skytte, Application Engineer Architect RF Summit, Espoo 2024

#### Overview

- Thermal Challenges

- Reliability

- Performance

- Design flow bottlenecks

- In-Design Enablement

- Thermal Analysis Options

- Microwave Office In-Design Thermal Analysis

- Summary

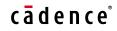

#### **Thermal Challenges**

#### Thermal Design – A Key Concern for Electronics Design

- Reliability / product life-time degradation

- Increased component stress

- Component parameter drift

- Open / short circuits

- Thermal run-away

- •••

- Performance degradation

- Nonlinearity

- Efficiency

- Increase in noise-sensitivity

- Device temperature bias mismatch

cādence

- Shortening burst duration

- •••

4 © 2023 Cadence Design Systems, Inc. All rights reserved.

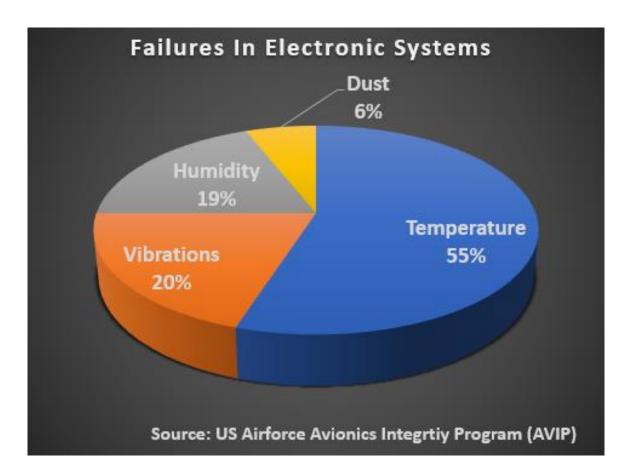

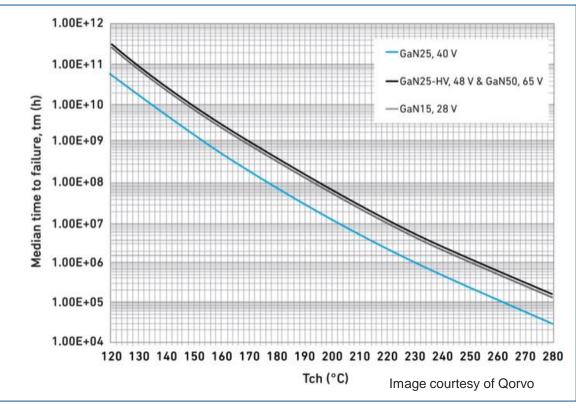

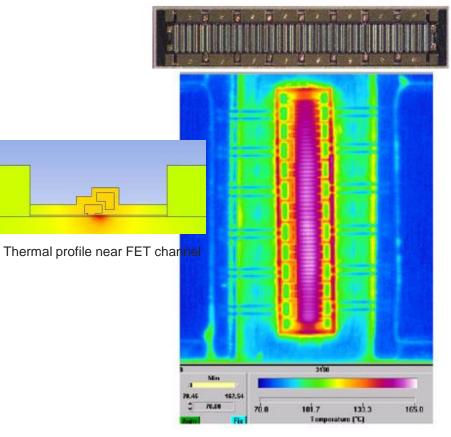

#### The Effects of Temperature On Electronics GaN HEMT High Power Amplifiers

• Time to Failure vs Temp

• Performance w / wo self-heating

#### Heat Generation in PAs

Typical Heat development in a GaN Power Amplifier

- A GaN HEMT with gate periphery of 28.8mm operating at 28 volts drain voltage delivers 120 Watts CW

- For 60% DC to RF conversion efficiency there will be 80 Watts dissipated heat

- For an active chip area of 2.5 mm<sup>2</sup>, the gate heat density exceeds 32 watts per mm<sup>2</sup> / 3.2kW per cm<sup>2</sup>

- This heat must be dissipated from the device channel through the heatsink and the package / and PCB so requires detailed analysis of the conduction path including the FET layout – this is not suited for traditional Thermal CFD simulations

Infrared thermal measurement of 28.8mm GaN HEMT Image courtesy of Cree

#### Status

- The Cost of Heating

- Reliability degradation / failure

- Performance degradation

- Heat mitigation is required

- Lower operating power reduces performance

- Impacts mobile & radar range, data rates, etc.

- Increase heatsinking

- increases cost, size, weight, complexity

#### Desired solution

• Address excessive heat with minimal mitigation to reduce impact on performance, costs, etc.

cādence

Minimize impact on engineering turnaround time

With these well known challenges, why is thermal analysis not done more regularly today in RF designs?

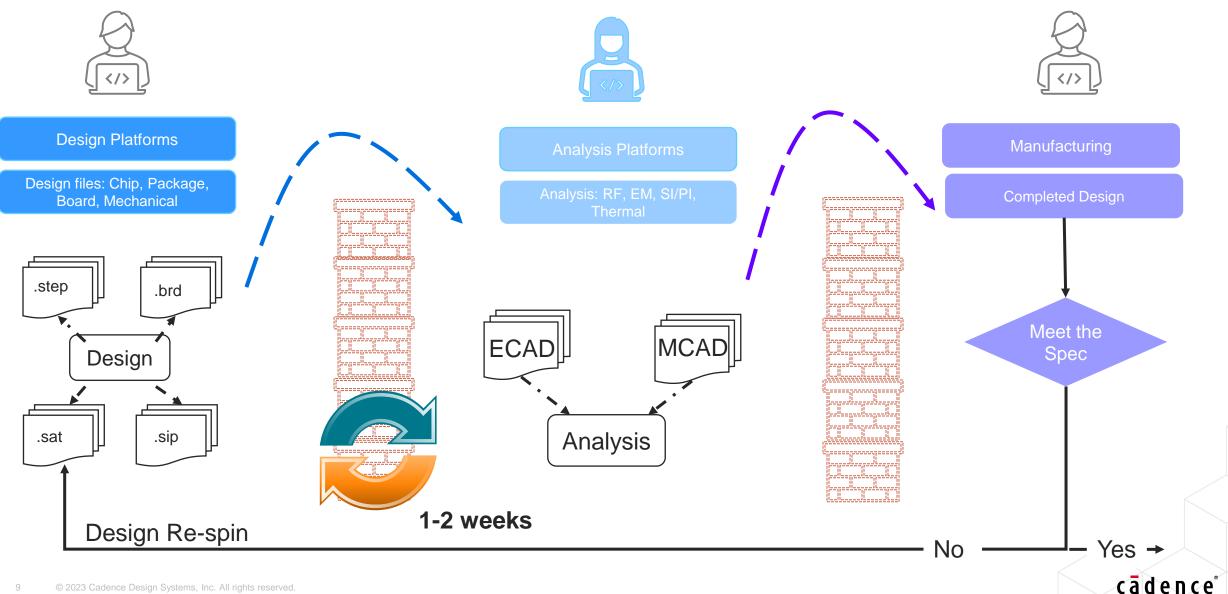

#### Multiple Platform and Lack of Workflow

#### Addressing this flow Bottleneck

- Enable RF engineers with ability to perform their own thermal analysis and optimize heat mitigation solutions during the design phase

- Requirements

- Accessible thermal analysis needs to be easy to use, easy to implement (set up), integrated in existing design flows

- Fast offer significant time savings over alternative (existing) approach

- Accurate proven thermal solver with high degree of confidence in results and resilient to user errors

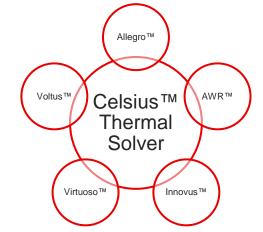

Celsius<sup>™</sup> Thermal Solver: Electrical-Thermal Co-Simulation A complete solution for unprecedented performance and accuracy

#### **Chip/PKG/System E-T Co-Simulation**

- Includes Chip/3DIC Analysis

- E-T Co-simulation

- Static and Transient

**Accuracy Beyond CFD**

- FEA-CFD integration

- 3D fluid-flow simulation

- Stress Analysis

- Electrical/thermal co-sim

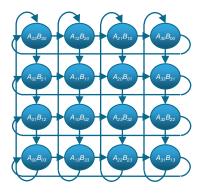

#### **Unprecedented Performance and Capacity**

- Massively parallel solver

- Linear scalability, cloud ready

- No loss in accuracy

#### Integration with Cadence® Design Platforms

- Single IC, 3D-IC

- Package, PCB

- Chassis, racks, systems

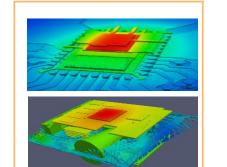

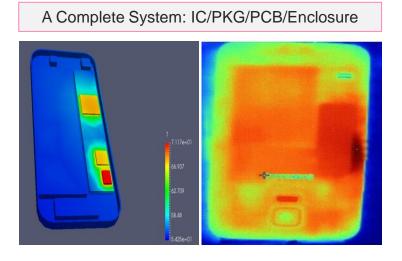

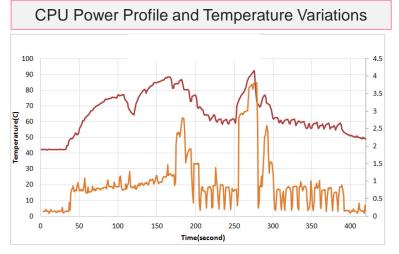

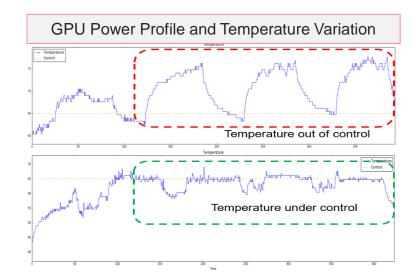

## Thermal Profiling in a Mobile Phone IC-centric electrical-thermal co-simulation - transient analysis and system optimization

| Transient thermal           | <ul> <li>Accurately calculate transient temperatures under various power scenarios</li> </ul>                                                                                     |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Thermal SPEC verification   | • Thermal runaway. CPU/GPU DVFS strategy for better thermal performance.                                                                                                          |

| Thermal sensor optimization | <ul> <li>Optimization of temperature sensors on chips for detecting thermal runaway</li> <li>Find Transient thermal hotspots with detailed power scenarios on each die</li> </ul> |

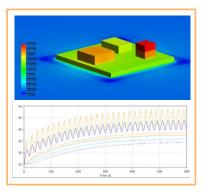

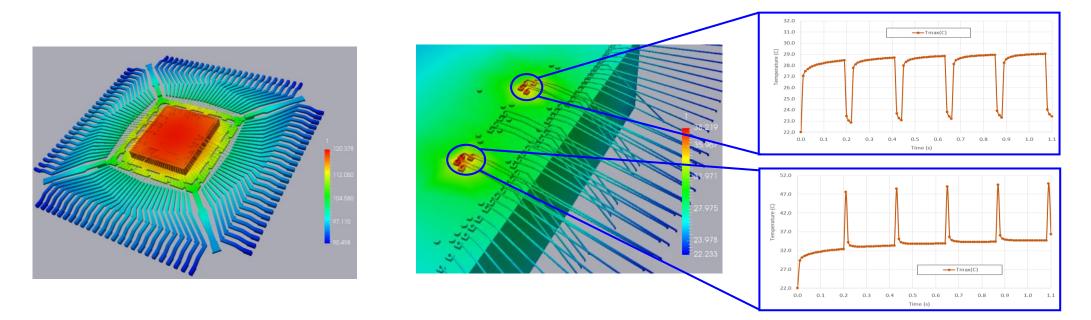

#### Advanced Lead-Frame Package and PCB Transient Electrical-Thermal Analysis with Resolution of 3D Configuration

| Design Import                 | <ul> <li>Package design imported from SiP layout</li> <li>3D structures created from SiP design</li> </ul>                                                                |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical-<br>Thermal Co-sim | <ul> <li>Detailed power profiling from chip simulation</li> <li>Additional power source from electric current</li> <li>Pulsed current going through bond wires</li> </ul> |

| Thermal Results               | <ul> <li>Transient and static analysis results generated</li> <li>Detailed temperature profiles on bond wires</li> </ul>                                                  |

#### In-Design Enablement

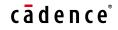

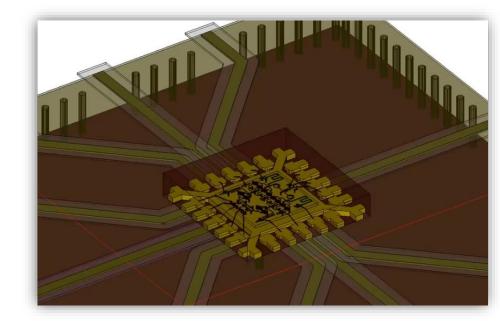

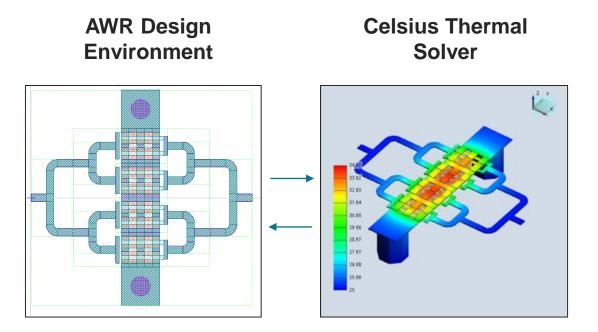

#### Thermal Extraction Setup – GaN FET Example

- Add extraction block to create thermal document

- New measurement creates power dissipation data file from nonlinear simulation

- Associate extraction block with stackup and power dissipation data file

- Simulate in Microwave Office<sup>®</sup> software or send to Celsius<sup>™</sup> Thermal Solver (native editor)

- Operating temps back-annotated into Microwave Office<sup>®</sup> and linked to user defined heat sources

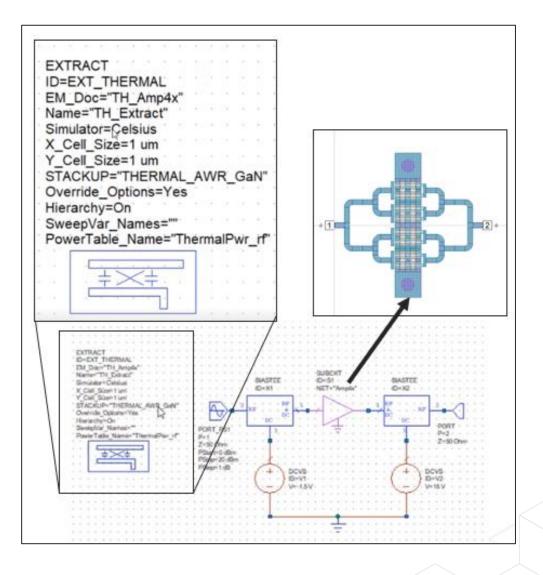

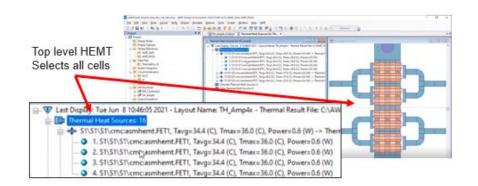

#### Thermal Analysis Results – GaN FET Example

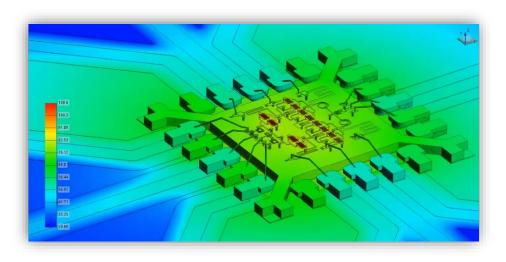

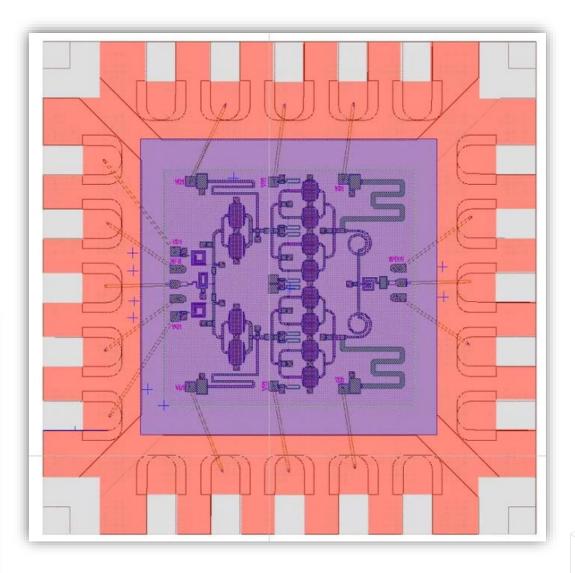

- Test structure GaN HEMT devices, combiner network and source to ground vias

- Celsius<sup>™</sup> Thermal Solver results automatically provides list of all defined heat sources throughout hierarchal design layout

- Selected thermal analysis results for individual heat source are highlighted in layout

- Average and peak temperature across heat source area and power dissipation are reported

#### Thermal Analysis Results – Multi Technology Example

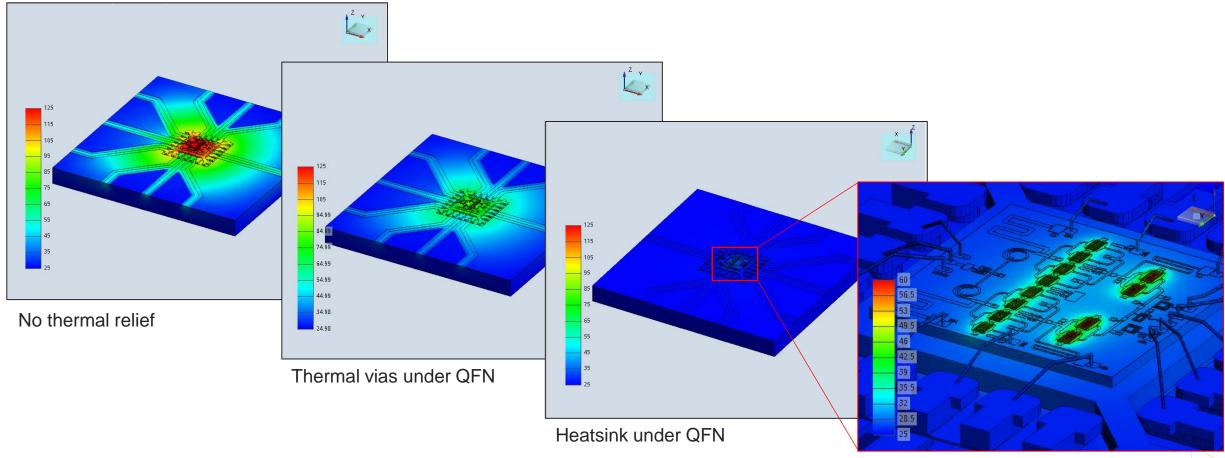

• Test structure – MMIC HPA in QFN package on PCB (identical temperature scale to 125 °C)

Enlarged view (60 °C temperature scale)

cādence

#### 7 © 2023 Cadence Design Systems, Inc. All rights reserved.

#### Please Contact us for a Demo!

## Celsius Thermal Solver for Thermal Analysis in Microwave Office Software

#### Key features and benefits

- Thermal structures are easily created using powerful Microwave Office<sup>®</sup> extraction block workflow

- Leverages existing structure data (geometries, materials, stack up) in Microwave Office software to define Celsius<sup>™</sup> structure

- Obtain power dissipation information from Microwave Office analysis

- Thermal simulations launched from inside AWR platform; results automatically returned

- Easy-to-use flow allows RF design engineers to perform their own thermal analysis

### Summary

#### Cadence RF Electrothermal = Speed, Accessibility, Accuracy

- Predicting thermal behavior of RF designs is very important to ensure reliability and performance

- Traditional flows for thermal characterization are too slow and error prone to provide design-side guidance

- AWR/Celsius integration

- Saves design re-entry

- Utilizes existing data structure in AWR as enable

- Provides near real-time access to critical thermal data using a sign-off quality thermal environment

# cādence

© 2023 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks of Cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks or Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks are the property of their respective owners.